DAC 2025: Navigating the Intersection of AI, Chiplets, and Sustainable Innovation

Frank Schirrmeister, #DAC62 Engineering Program Chair, Synopsys,

Returning to San Francisco’s iconic Moscone Center, DAC will mark its 62nd edition from June 22-26, 2025. It is the premier global event for semiconductor design and electronic system innovation – the “Chips to System Conference.” DAC continues to be the compass orienting the electronic design community towards the most transformative industry trends.

In 2025, DAC’s narrative will be distinctly shaped by three interconnected forces: Artificial Intelligence (AI), Chiplets, and Sustainable Innovation. These pillars are interconnected and collectively redefine how we approach electronic system design. You will find some key links at the end of this Blog.

AI Takes Center Stage—A New Design Era Emerges

It’s no exaggeration to say that AI will be part of almost every discussion at DAC 2025. Conference highlights clearly signal AI’s dominance as the single most influential technology reshaping the landscape of electronic design and the conference will cover both AI for design and design for AI silicon and systems. AI is an enabling fabric at the core of the entire connected design ecosystem, fundamentally altering how designs are conceptualized, validated, and optimized.

The three conference keynotes underscore this integration. William Chappell of Microsoft will explore on DAC Monday the emergence of reasoning agents—AI-driven entities capable of autonomously refining chip designs. On Tuesday, AMD’s Michaela Blott will discuss how hardware advancements facilitate the expanding AI revolution. And UCLA’s Jason Cong will illustrate on Wednesday how deep learning democratizes access to sophisticated design methodologies, potentially revolutionizing who can engage in advanced semiconductor development.

In addition, Tech Talks, SKY Talks and some of the Engineering Track Special Sessions address the practical implications of AI integration—from improving security through Large Language Models (LLMs), optimizing EDA tool performance, to innovating R&D practices. Clearly, AI is not just a conference buzzword but is driving the industry towards greater design agility and innovation.

Some of the AI highlights include “Generative AI in Design & Verification: Are We Hallucinating or Innovating?” in the DAC Pavilion on Monday and “AI-Enabled EDA for Chip Design” and “LLM Innovations: Mirage or Milestone ?” on Tuesday in the Engineering Track, as well as “AI and VLSI: A Symbiotic Revolution Enriching Our Lives and Shaping Our Future” in the DAC Pavilion. On DAC Sunday, Arm’s Mohaman Awad will kick off the series of SKYTalks at 5 pm asking “The AI Imperative: What Will We Make of This Moment?” And Tuesday morning will see the Research Special Session organized by Meta called “AAA: Advanced AI Accelerators” highlighting some of the AI architectural trends. The three days of DAC will have many, many more AI related sessions, which you can find in the DAC62 Conference Program by filtering for AI as topic.

Chiplets: Modular Architectures Rewrite the Rules

Alongside AI, multi-die design using chiplets represent not only the industry’s response to the increasing limitations and costs of traditional monolithic System-on-Chip (SoC) approaches, but also offer ways for performance optimization, flexibility and customization, efficiently addressing Moore’s Law limitations.

Addressing this architectural shift, DAC 2025 features together with EETimes the “Future of Chiplets Pavilion,” explicitly themed “Building Chiplets for the AI Era.” This emphasis reflects an acknowledgment that next-generation systems—particularly those underpinning AI workloads—demand the flexibility, scalability, and efficiency only achievable through chiplets.

The substantial presence of chiplet-specific programming and content throughout the technical sessions reinforces their importance. Chiplets are not just an alternative to traditional integration—they are the strategic choice for achieving differentiated, high-performance systems capable of meeting tomorrow’s AI-driven demands.

Some of the must-attend sessions include “Next Generation UCIe: Enabling a Thriving Open Chiplet Ecosystem” and “Enabling Multi-Die 3DIC Designs with AI-Powered Ecosystem Collaboration” on Monday morning in the Engineering Track and the Panel discussion “Developing the Chiplet Economy” on Tuesday at 2pmin the Chiplet Pavilion. Again, you can find many more in the DAC62 Conference Program. In the Research Track, “Chiplet-based Heterogenous Integration: Pushing Beyond Moore's Law” will update Tuesday afternoon at 3:30 pm on the latest research trends around packaging, materials, and EDA for heterogeneous integration.

Sustainable Innovation: A Critical Design Criterion Emerges

DAC 2025 brings sustainability into focus as the industry grapples with its environmental footprint, highlighting the urgency to embed eco-friendly practices within semiconductor design and manufacturing processes.

Notably, Serge Nicoleau of STMicroelectronics integrates in his SKYTalk “AI Booster for R&D, Edge Computing, Chiplets, and Sustainability” on Wednesday at 1 pm sustainability directly with AI, edge computing, and chiplets, suggesting a nuanced perspective: advanced technologies, though energy-intensive, can also contribute significantly to sustainability objectives. AI-driven optimization, energy-efficient chiplet architectures, and edge computing to reduce data transmission energy demands exemplify how technological advancement itself can be aligned with sustainability goals.

Sustainability at DAC isn’t framed merely as a challenge, it’s presented as a strategic opportunity—a catalyst for innovation and differentiation in design.

Technical Program and Exhibition: Innovation at Scale

DAC’s extensive technical program, with over 350 presentations, showcases the research and engineering communities driving the future of electronics. We had significant increases in submissions to both Research and Engineering tracks, so attendees can expect lots of new insights. The poster gladiator sessions in the DAC Pavilion highlighting short presentations from key selected poster s every day towards the end and have become an attendee favorite.

The future of the industry discussing trends like Quantum will be discussed in research special sessions like “Advancing Quantum Computing for Tomorrow,” with some promising to venture out 20 years, like the “IEEE Council on EDA Distinguished Panel - 20th Anniversary Panel: AI Hardware & EDA, the next 20 years: Smarter, Taller, Deeper,” featuring some of our favorite EDA and System Design luminaries.

The exhibition floor, featuring approximately 150 companies, further enriches attendee experiences and allows attendees the future that was described a couple of DACs ago by showcasing the latest product releases.

The Bottom Line: Don’t Miss DAC 2025

With the electronics industry at such an amazing stage – I don’t know about you, but my family started caring about semiconductors just a couple of years back and now my job is finally “hip” - shaped by the convergence of AI, chiplets, and sustainability, DAC 2025 represents a uniquely critical gathering.

For anyone in electronic design—be it strategy, innovation, or execution— DAC is indispensable, not only highlights the future—it actively shapes it.

See you next week in San Francisco!

Here are some fun links to prepare:

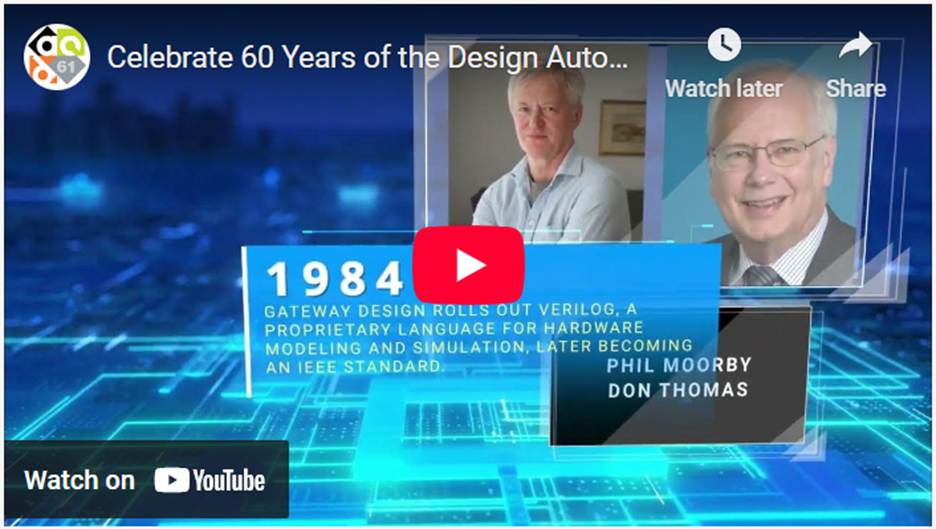

To get into the mood for DAC, this video highlights 60 years of innovation that got us here. Definitely worth watching!

You can still register here.

You can build your agenda using the Full Conference Program, the Exhibitor Forum and the EETimes Chiplet Pavilion